I ran a 30 minute gaming session on an issue 4 board inside a ZX NEXT case, playing:

Nothing (128K @ 28 MHz) Galaxy of Errors (ZX NEXT) Warhawk (ZX NEXT) Delta's Shadow (ZX NEXT) The Next War (ZX NEXT)

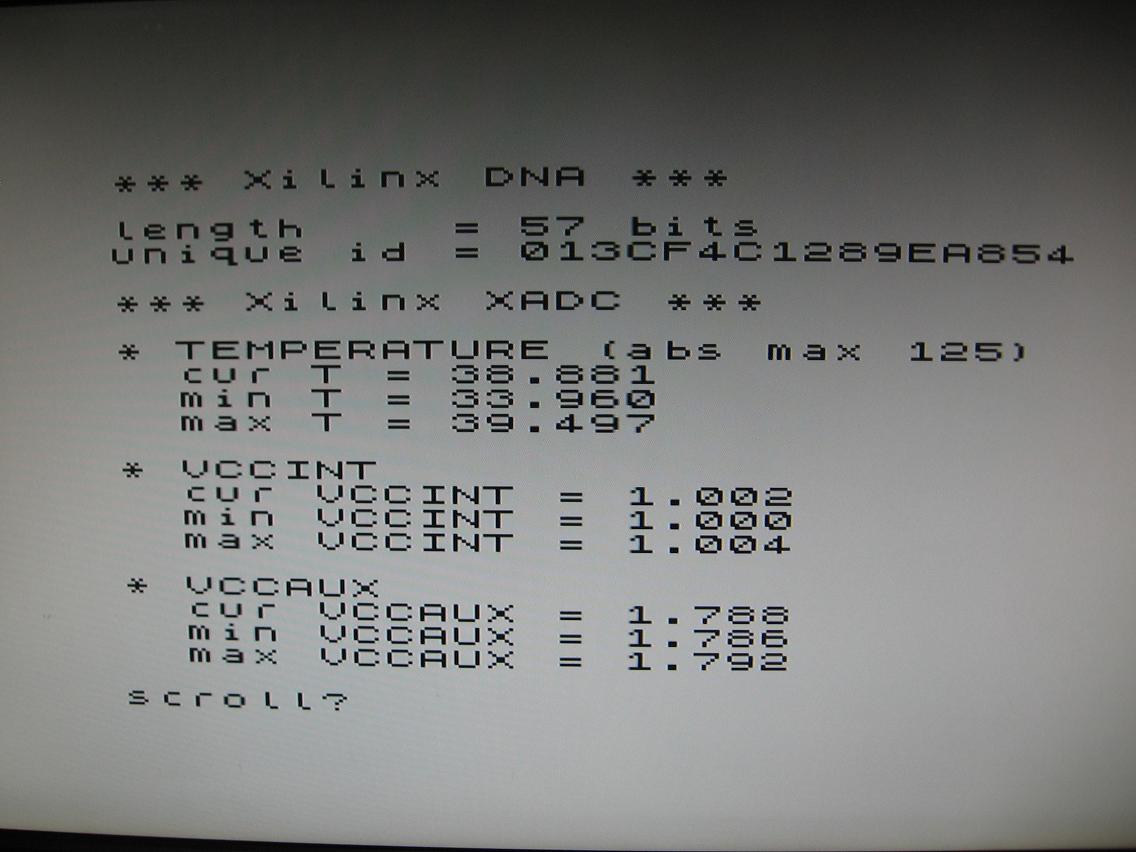

.xper -dx produced:

Error in the temperature sensor is +- 4 C and error in the voltage sensor is +-1% (see DS181 Artix 7 data sheet, page 57).

Room temperature was about 26 -27 C last night with the Next reporting initial temperature of 30 C; that would suggest an error of +3 C at least initially. I think the error I've seen with this fpga is actually smaller than that because we don't get to see the temperature readings accumulated by the anti-brick core which initially runs after power up. The fpga very quickly warms up to a steady temperature after power on. So the XADC temp recorded may actually be closer to 26- 27 C while the anti-brick core runs but by the time the ZX NEXT core is booted (which clears accumulated data), the fpga has already warmed up to an idle temperature.

VCCINT is regulated at 1 V and VCCAUX at 1.8 V. (Not shown) VCCBRAM is regulated at 1 V.

Complete source and xper binary can be downloaded from: